## SMT HF SDR S/H (Sample and Hold) Receivers DR2G from 30 kHz to 70 (100) MHz - Make it Simple as Possible with Outstanding Performances

## Dipl. Ing . Tasić Siniša – Tasa YU1LM/QRP

All rights reserved, project is free for personal use only

I started publishing my SDR series with wish to reject common opinion that isn't possible achieve and realize good performances without new, latest modern components. I also tried to enable new SDR technology for people from "third world ",easy and repeatable design without any RF experience and design for people which aren't SMT components lower. I also have a big collection classic size through holes components which ware reduced my design coast and enabled me endless experimenting. I have to admit that the new modern components have much better performances and designs are much more predictable than with old one. Professionally I am using SMT components but it is hard to design something new without appropriate PCBs. Experimenting with SMT resistors and capacitors are much more simple and quickly that with classic size components when we have PCB.

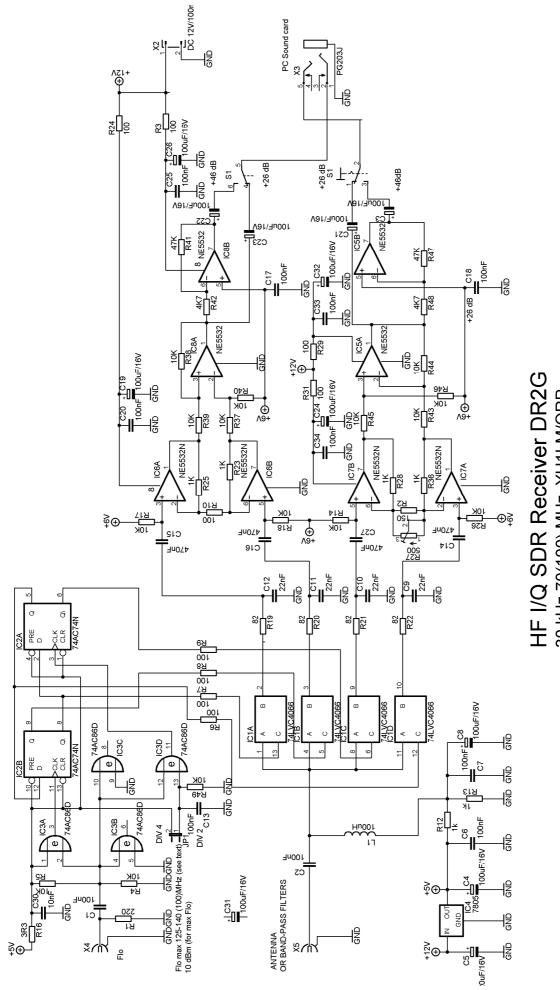

This new SDR DR2G receiver is my try to make simple as possible but very respectable performances SMT SDR receiver with two working modes optimal (4 times higher LO frequency) and non-optimal (LO twice higher). Optimal region is for lower frequencies to 50 MHz where we have need for much better RX performances demands that they are at higher frequencies. The double side PCB (one side back side is complete GND layer) was specially designed that it is possible their realization without metallization VIAs with few jumpers from back side only (see pictures inside text). This is also receiver which with new 74LVC\*\*\* series components can work to the 100 MHz without input band pass BP filters. I tried it to 75MHz because I couldn't find EXOR IC 74LVC86. I also enabled that we can use classic electrolytic capacitors instead SMT which is sometimes hard to find in adequate size.

DR2G design is compilation of different designs. It is based on previously published receivers DR2E, DR2A+ designs. The 74LVC4066 as main S/H elements has Rds-ON resistance in region 3-5 Ohms and their frequency limits is over 100 MHz range. IC FF 74AC74 is working to 140-145 MHz better substitute 74LVC74 works to 250MHz and EXOR 74AC86 to 140MHz 74LVC86 to 180-200 MHz.. These ICs are determining DR2G overall performances. New better ICs enable much better performances and matching between switches in S/H detector circuit and because of that better hardware image rejection. Small Rds-ON is enabling better input IP3. Non optimal work in divide by 2 mode it isn't critical as it is with the old classic size components only it is important that input LO amplitude is high enough to enable correct dividing. Because of non optimal work good LO signal with close to the ideal sinusoidal shape or digital LO with 50/50 % ratio will enable good work in appropriate image rejection. It is important that is possible with resistor 10K\*\* to the GND net at LO input make fine adjustment close to the max LO frequency to adjust maximum image rejection.

If we are using 74LVC74, for max input LO frequency, max power voltage supply have to be +3.3V. It is necessary to substitute 7805 with three terminal 3.3V voltage regulator.

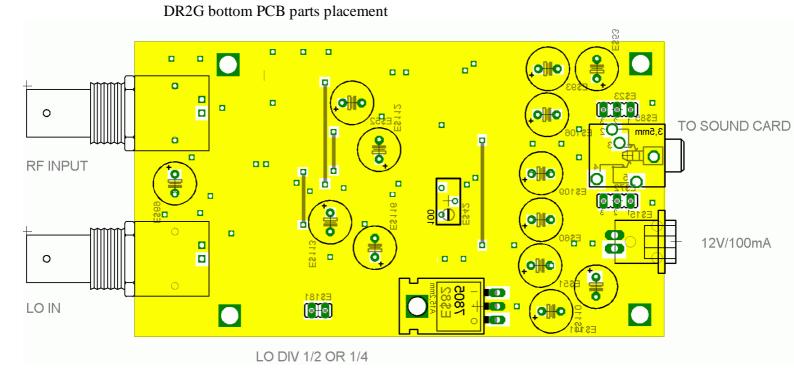

LO DIV 1/2 OR 1/4

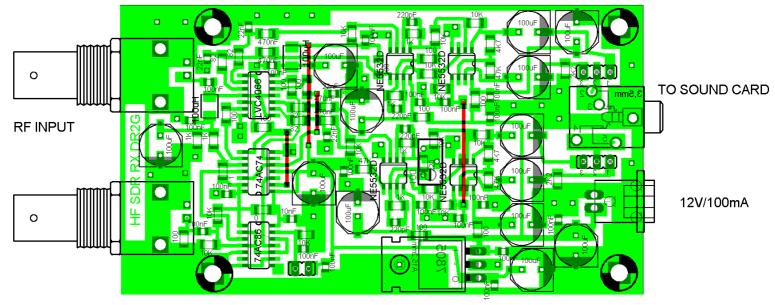

DR2G top PCB elements placements

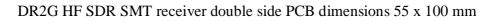

LO DIV 1/2 OR 1/4

DR2G bottom PCB parts placement with classic through-hole ELCO

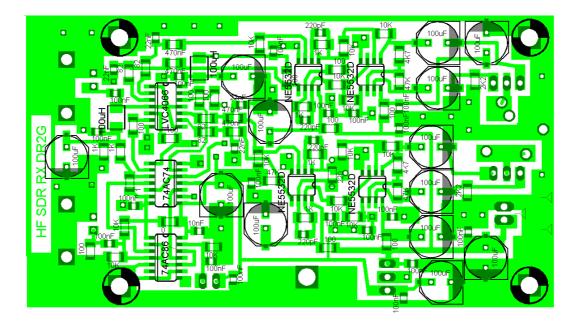

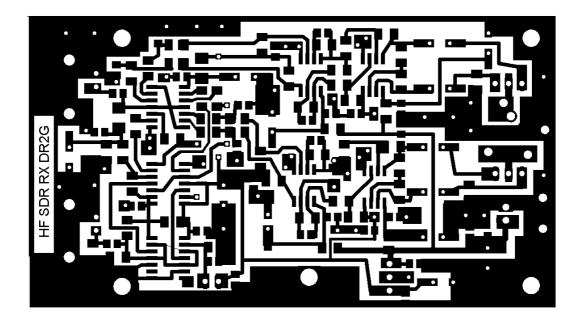

DR2G top PCB

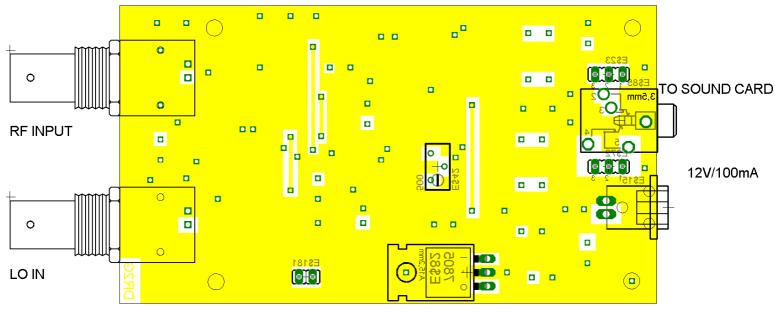

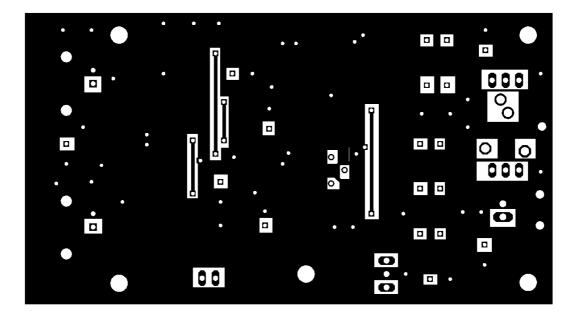

DR2G bottom PCB

30 kHz-70(100) MHz YU1LM/QRP

DR2G montage process if you haven't PCB with VIAs

- 1. First it is necessary with borer diameters bigger then VIA's drill bottom copper surface to remove it at VIA's "hot" points to prevent unwanted connections.

- 2. Next step is to solder wires at VIA places at both side and cut it close as possible to surfaces

3. Then solder 4 wires from bottom size to enable correct connection (DRG bottom PCB parts placement)

- 4. Next step is to solder SMT components from top side

- 5. Last step is to solder components at bottom side

VIAs and bottom side wires connection

DR2G process adjustments are simple and done in two steps:

- 1. With 500OHms potentiometer adjust with DMM (digital multi meter) that is resistance 100 Ohms.

- 2. Second step is to with 5000HMs potentiometer in SDR software adjust max image rejection

Measuring results which I made with HF S/H SDR receiver DR2G

- 1. Receiving range from 30 kHz to 70(100) MHz.

- 2. IIP3 34-37dBm and it depends from setting and used programs.

- 3. MDS -120-122dBm also with 24 bit external USB SB card Audigy NX2

- 4. Image rejection is from 35 -65 dB

- 5. Sensitivity 0.3 0.6 uV for 10 dB S/N ratio, max S/N ratio I measured was 75 dB.

- 6. SFDR (Spurious free dynamic range) is 95-98 dB, this results are with signals spaced 5 kHz and more.

Some excellent performances aren't without other side:

- 1. First and very big disadvantage is 4 or 2 times higher LO

- 2. Image rejection is changing through receiving bands and results are done for frequencies 12 kHz from central frequency

I wish you successful DR2G realization and I apologize for some possible mistakes. I made great effort to make SDR projects and share them with all who are interesting for. Anyway send me your comments positive or negative, results or photos of your realization please.

VY 73/72 and GL in SDR homebrew Tasa YU1LM/QRP

April 2008 corrected PCB with some pictures realized RX and measurements done by builders!

DR2G built by Antarius

## Parts from Joao's CT1FGW(ex CR6FY, ZS1JPC) E-mail about DR2G

I build one of your SDR receivers, the DR2G with the intention of using it as an IF for a 8.3GHz DNS receiver that I have. My receiver IF output is from 60 to 80MHz and so I used the LVC IC's and 3.3V regulator.

Unfortunately the 74LVC74 that I received is a TSSOP package and I can not fit it to the board, so I fitted a 74AC74 for the meantime to test the receiver.

My first test was a bit disappointing as there was no image rejection at all. I checked the outputs of the 7474 and they looked all right, two sets of outputs at 90° and 180° to each other but the sine waves output of the receiver were absolutely in phase. I found out that even though the diagram is correct the PCBoard is not. The pins 5 and 6 of the 7474 are swapped, after the change to PC Board I got an impressive image rejection, using the software correction (winrad and winradhd) I got more than 70dB.

I am very impressed with the receiver as a whole, I have been a HAM since the early 60's, I like to build equipment and don't get impressed easily. This is my first attempt at I/Q SDR even though my first SSB rig was a phasing type TX (in the 60's).

I still do not have a LO for it, I am using my signal generator at the moment. I can suppress the image to practically nothing (well over 70dB) but if I change bands the suppression changes a lot.

Software correction:

| LOx2 | 7.110MHz | amp 0,962 | phase -0,065 |

|------|----------|-----------|--------------|

|      | 14.110   | 0,954     | -12,096      |

| LOx4 | 7.110    | 0,992     | -1,466       |

|      | 14.110   | 0,992     | -2,067       |

The problem is with the phase, I am very used to the frequency dependence with the circuits we used in the 60's, because we used tuned circuits to obtain the 90° rotation of the RF, I did not expect this from a digital circuit,. Do you also experience this problem or do I have something wrong?

This could be sorted very easily if the software had a set of corrections for each band, but the software I am using does not have this (winrad and winradhd) maybe its only me with this problem?

The second problem is the LO leakage. I was so happy with the RX that I went to connect it to the VHF rig, branching the IF out right after the first mixer (10.8MHz) for the SDR. Unfortunately the LO completely overwhelms the receiver. The only solution I see is to convert the 10.8 to some other frequency before applying the signal to the SDR. I also thought of making an isolating amp (maybe a JFET with a grounded gate?) but the signal is so strong that I have my doubts if it solves the problem.

Here are the measurements of the leakage:

| LOx4 at 56MHz |               | LOx2 at 28MHz |               |  |

|---------------|---------------|---------------|---------------|--|

| 14MHz<br>28   | -46dBm<br>-72 | 14MHz<br>28   | -46dBm<br>-58 |  |

| 20            | -12           | 20            | -20           |  |

| 42            | -50           | 42            | -50           |  |

| 56            | -42           | 56            | -42           |  |

This is measured at the antenna connection feeding the LO with +10dBm (actually the LO level does not make any difference until it drops out at about -10dBm when the gates stop working).

The leakage goes all the way to the microwaves (to at least 4GHz) HI. a low pass filter in the input is a must.

My comment results are that they are strictly depend in 2x LO mode from input LO shape. If it is closer to the 50-50-% ratio results are very good. In 4 x LO mode phase errors is increasing with frequency what is normal reason is finite speed of used ICs! With higher LO frequency we have bigger delay and bigger phase error!

New E-mail address tasayu1lm@gmail.com tasa@insimtel.com

**References:**

- 1. <u>www.qsl.net/yu1lm/homebrew</u>

- 2. http://forum.cqham.ru/viewforum.php ?f=28

- 3. <u>Skidan@mail.ints.net</u> T03DSP UR3IQO <u>http://users.ints.net/skidan/T03DSP</u>

- 4. <u>http://www.nitehawk.com/sm5bsz</u> Leif LINARD

- 5. <u>http://www.flex-radio.com</u> SDR1000 Gerald AC50G

- 6. <u>http://www.njqrp.org/mbrproj/9850dds.html</u>

- www.analog.com/en/prod/0,,770\_843\_AD9850,00.html

http://www.qsl.net/pa3ckr/signalgenerator/

http://www.k6ese.com/DDS\_Project.htm

http://ham.kiev.ua/pic/dds\_ham2.html

http://www.qsl.net/om3cph/dds/rx.html

http://www.seboldt.net/k0jd/othervfo.html

http://perso.wanadoo.fr/f6itv/p2063001.htm

http://koti.netplaza.fi/~jonverro/ad9854.htm

http://www.labyrinth.net.au/~steve/freq/

http://members.aol.com/Dl4JAL/DDS.html

http://hem.passagen.se/communication/dds.html

- 7. Recent Advances in Shortwave Receiver Design Dr. Ulrich Rohde QST Nov 1992 page 53

- 1. RF Design 6/1995

- 2. Philips- Application note AN97090( IC gate overtone oscillator design)

Software LINK for SDR radio receiving and transmitting

- 1. <u>http://digilander.libero.it/i2phd/</u> SDRadio software ver 1.0 www.qsl.net/i2phd Alberto I2PHDhttp://gpsdo.i2phd.com/

- 2. ik2czl@weaksignals.com <ik2czl@weaksignals.com>ik2czl@weaksignals.com <<u>ik2czl@weaksignals.com</u>>Vittorio

- 3. www.weaksignals.com WINRAD

- 4. www.ciaoradio.com

- 5. www.m0kgk.co.uk/sdr

- 6. www.g8jcf.dyndns.org Peter G8JCF

- 7. <u>http://www.nitehawk.com/sm5bsz</u> Leif LINARD

- <u>http://www.flex-radio.com</u> SDR1000 Gerald AC5OG

dl6iak.ba-karlsruhe.de